- 您现在的位置:买卖IC网 > Sheet目录3872 > PIC18F4450T-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX16 44QFN

61

XMEGA A [MANUAL]

8077I–AVR–11/2012

Notes:

1.

For DAC only, channel 0 and 1 exists and can be used as triggers.

2.

Channel 4 equals ADC channel 0 to 3 all together.

Note:

1.

CC channel C and D triggers are available only for timer/counters 0.

0xAA

SPIF

SPI F DMA trigger value

0xAB

USARTF0

USART F0 DMA triggers base value

0xAE

USARTF1

USART F1 DMA triggers base value

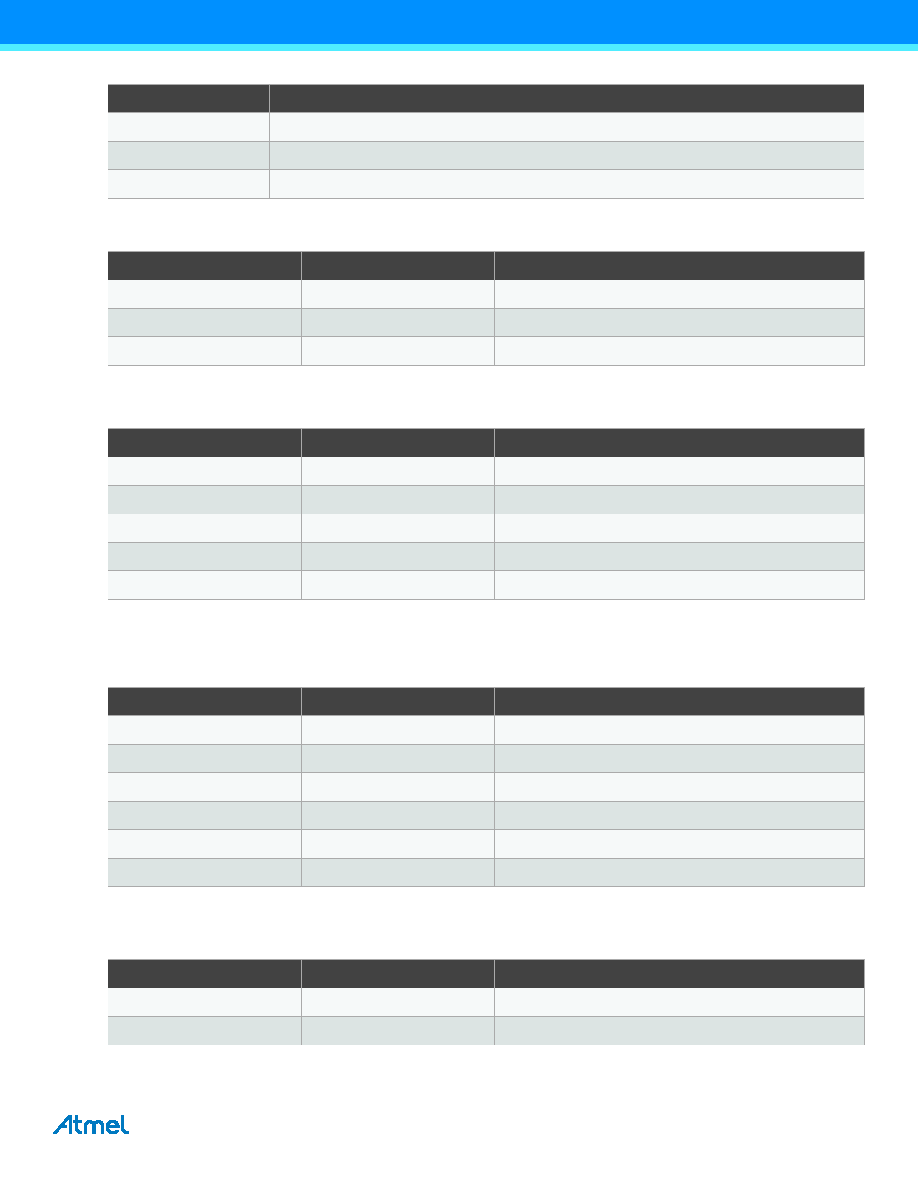

Table 5-10. DMA trigger source offset values for event system triggers.

TRGSRC Offset Value

Group Configuration

Description

+0x00

CH0

Event channel 0

+0x01

CH1

Event channel 1

+0x02

CH2

Event channel 2

Table 5-11.

DMA trigger source offset values for DAC and ADC triggers.

TRGSRC offset value

Group Configuration

Description

+0x00

CH0

ADC/DAC channel 0

+0x01

CH1

ADC/DAC channel 1

+0x02

CH2(1)

ADC channel 2

+0x03

CH3

ADC channel 3

+0x04

CH4(2)

ADC channel 0, 1, 2, 3

Table 5-12. DMA trigger source offset values for timer/ counter triggers.

TRGSRC Offset Value

Group Configuration

Description

+0x00

OVF

Overflow/underflow

+0x01

ERR

Error

+0x02

CCA

Compare or capture channel A

+0x03

CCB

Compare or capture channel B

+0x04

CCC(1)

Compare or capture channel C

+0x05

CCD(1)

Compare or capture channel D

Table 5-13. DMA trigger source offset values for USART triggers.

TRGSRC Offset Value

Group Configuration

Description

0x00

RXC

Receive complete

0x01

DRE

Data register empty

TRIGSRC Base Value

Group Configuration

Description

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F4321T-I/ML

IC PIC MCU FLASH 4KX16 44QFN

PIC18F4221T-I/ML

IC PIC MCU FLASH 2KX16 44QFN

PIC18F2321T-I/ML

IC PIC MCU FLASH 4KX16 28QFN

PIC18F2221T-I/SO

IC PIC MCU FLASH 2KX16 28SOIC

PIC16LF1939-I/MV

IC MCU 8BIT 28KB FLASH 40-UQFN

PIC24F16KL402-I/SP

IC MCU 16BIT 16KB FLASH 28-SPDIP

PIC18F24J11-I/SS

IC PIC MCU FLASH 16K 2V 28-SSOP

PIC24F16KA101-I/SO

IC PIC MCU FLASH 16K 20-SOIC

相关代理商/技术参数

PIC18F4450T-I/PT

功能描述:8位微控制器 -MCU 16KB FL 768 RAM 34 I/O FS-USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-BL

制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB; Silicon Manufacturer:Powerlite Systems; Core Architecture:PIC; Kit Contents:Board; Features:Bootloader Programming, RS232 Connector for Boot-Loading and Serial Comms ;RoHS Compliant: Yes

PIC18F4455-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/P

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4458-I/ML

功能描述:8位微控制器 -MCU 24KB Flash 2KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT